水若善上

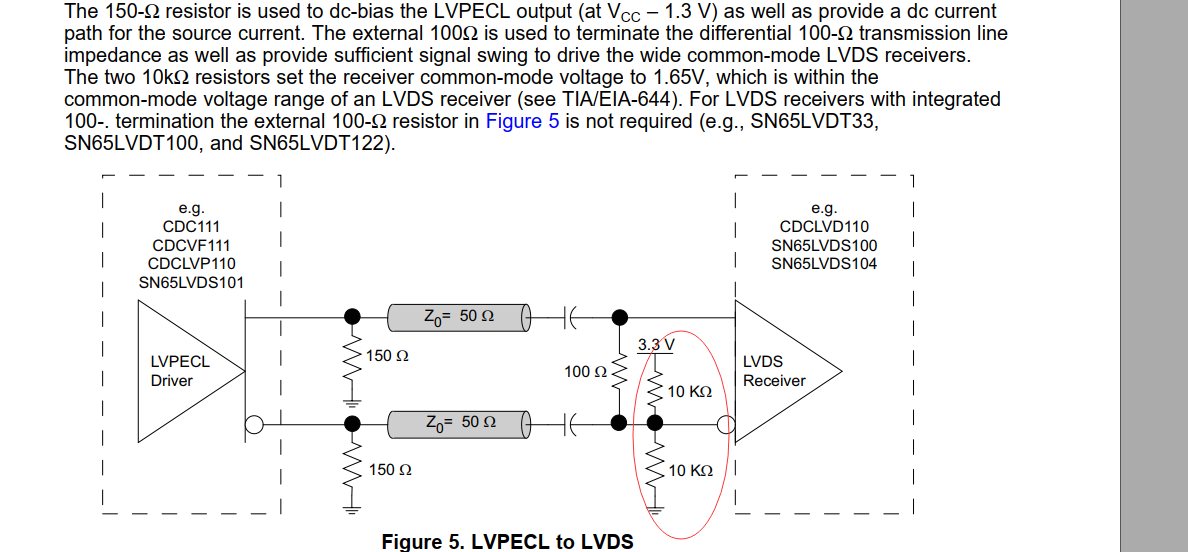

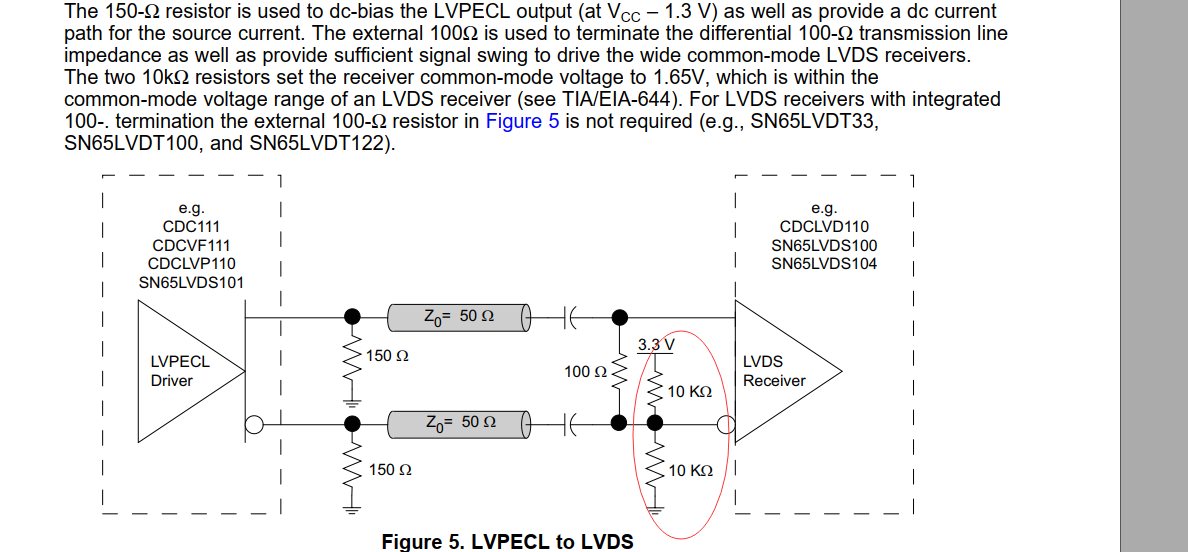

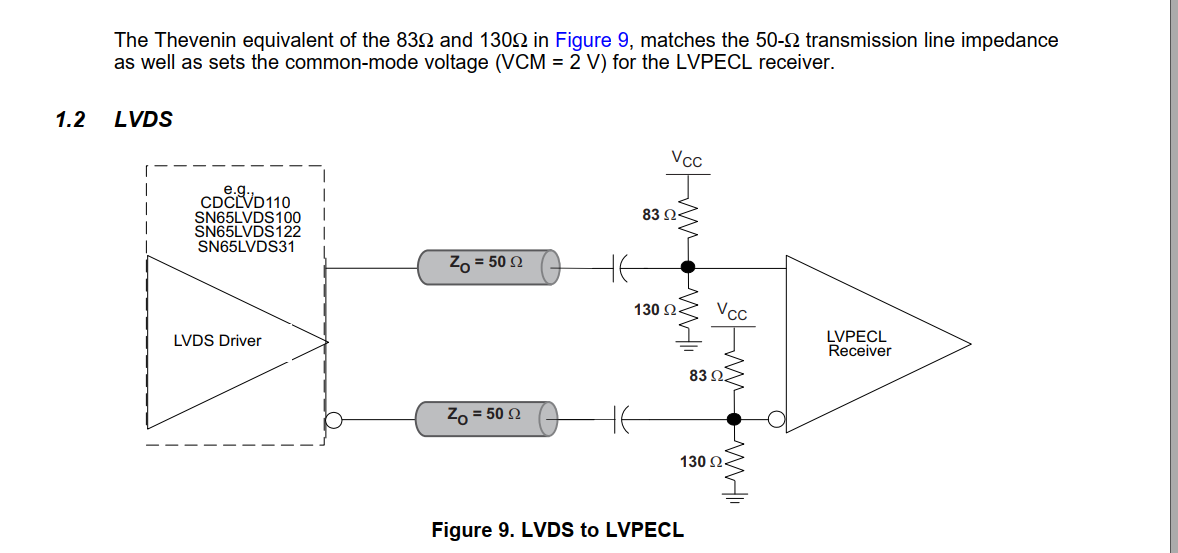

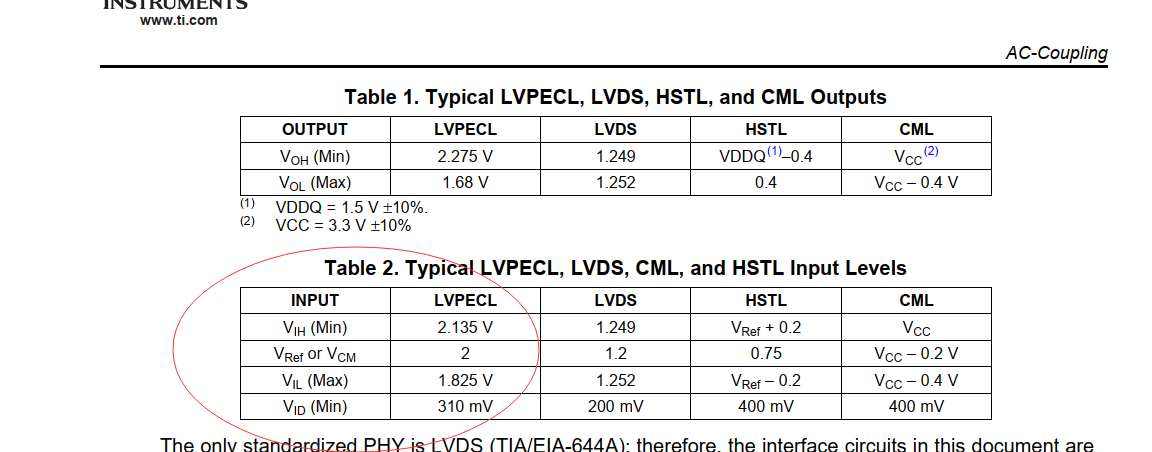

?After future 我要做一个LVDS和LVPECL的电平转换电路 第一个?的就是这个为啥只加在负极

第一个?的就是这个为啥只加在负极

水若善上

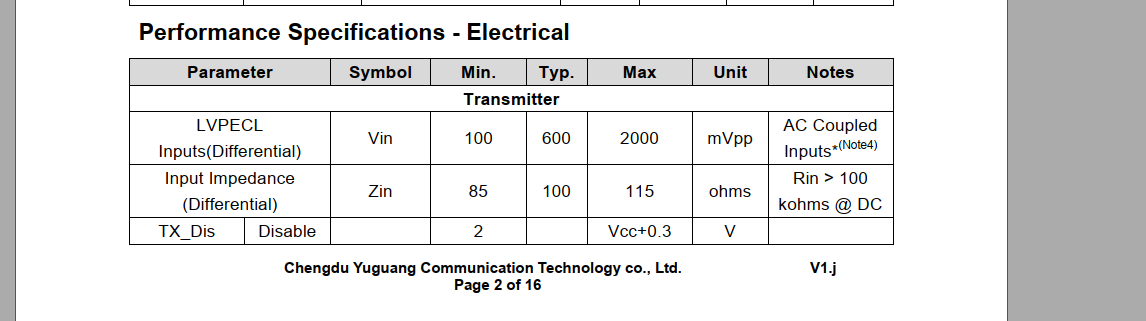

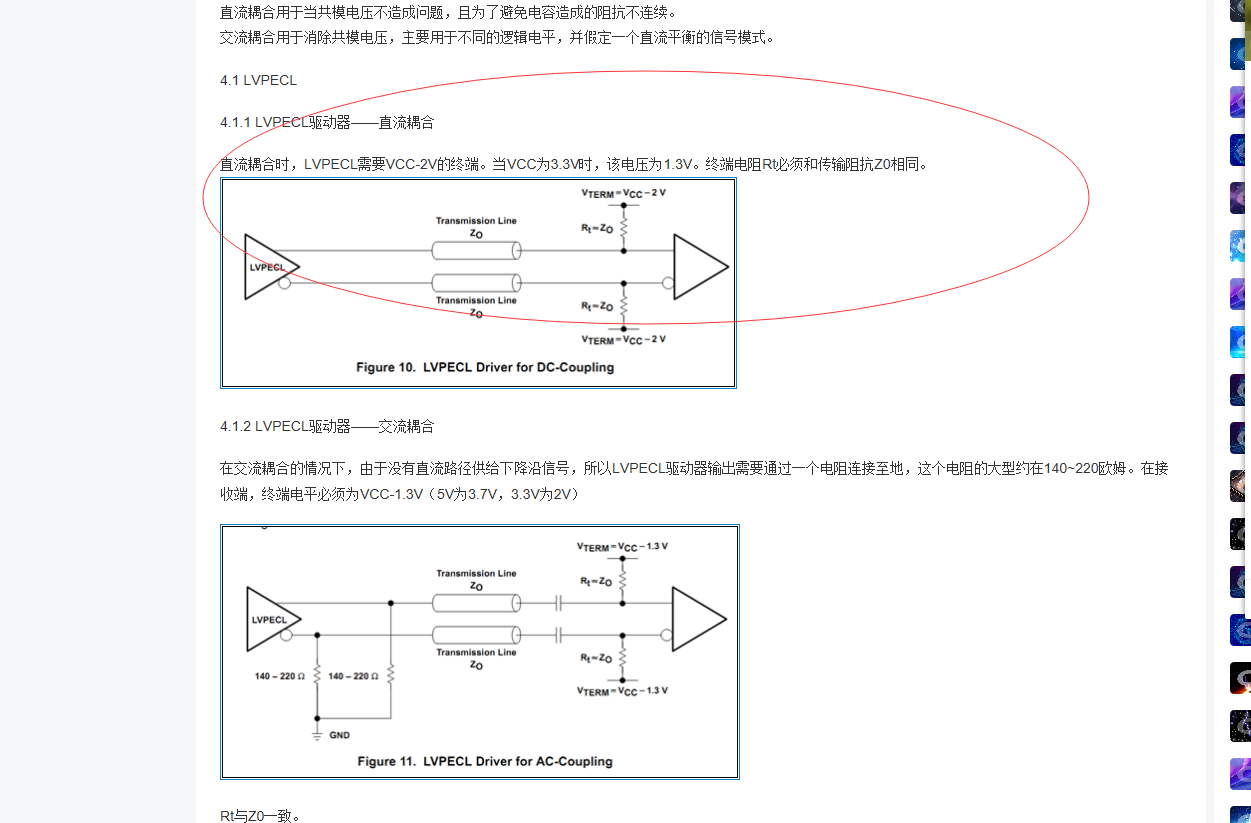

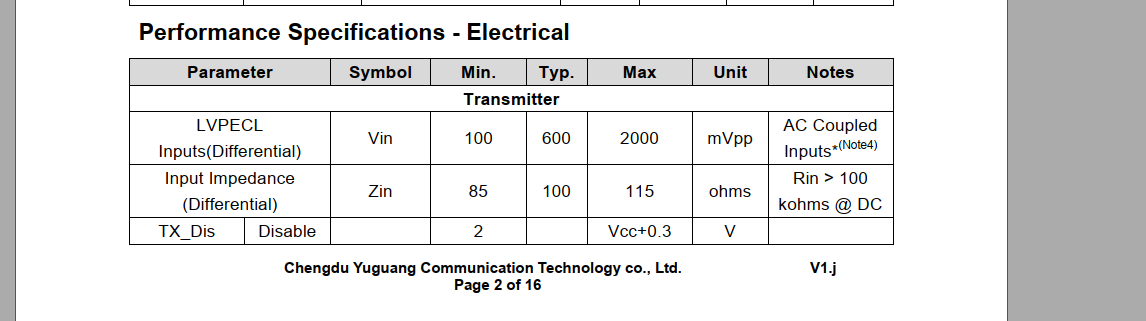

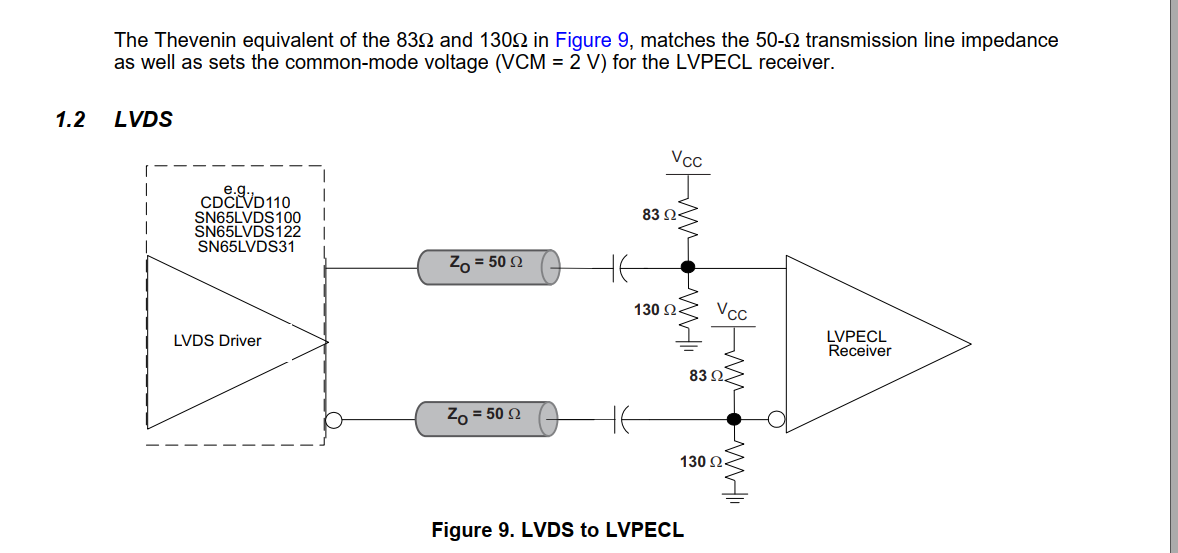

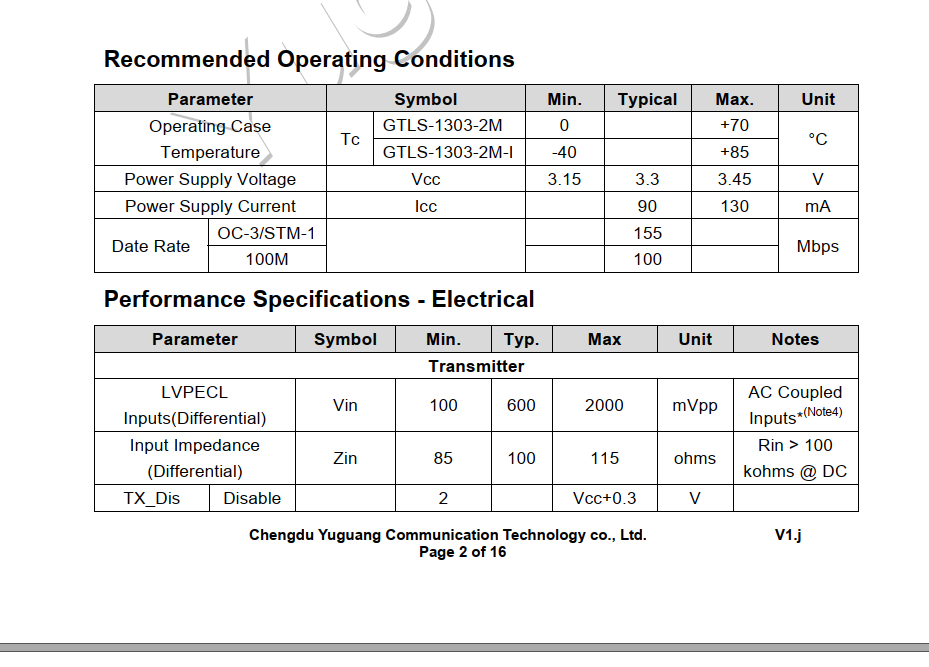

应用场景是FPGA直接到光口3V3电源 光口手册如图两对差分线一对LVDS转LVPECL一对LVPECL转LVDS

光口手册如图两对差分线一对LVDS转LVPECL一对LVPECL转LVDS 醒醒夏

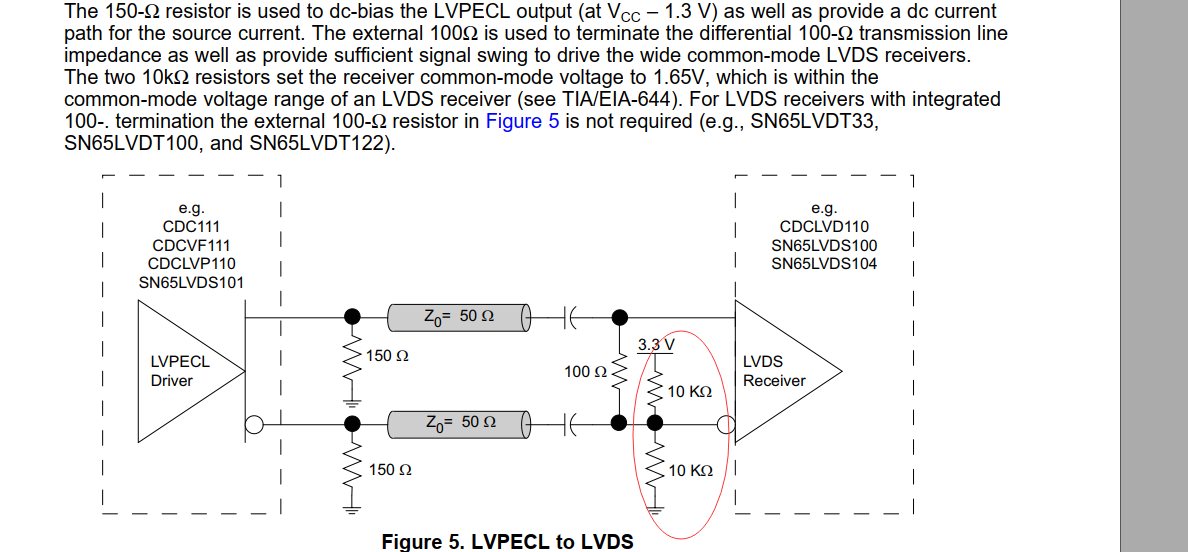

单电源供电当然要给负向输出端提供直流偏置

全差分运放输出Vo+=Gain*Vi/2+Vcom; Vo-= -Gain*Vi/2+Vcom;

醒醒夏

具体的要看看你这个接收器LVDS的datasheet

水若善上

?夏醒醒 LVDS接收端是FPGA芯片,国产FPGA

醒醒夏

?上善若水 具体看看LVDS输入端模块框图

大概意思就是我上面说的

?旭日东升 不搞啊

我们公司别的同事负责高速 所以我一直没弄

?上善若水 你发送端啥供电?

也是3.3V?

升东日旭

这个只是一个偏执电压,放正端,负端,中间,都一样,只要能进去就行。一般FPGA的LVDS都是标准的,这个偏执电压可以不要

水若善上

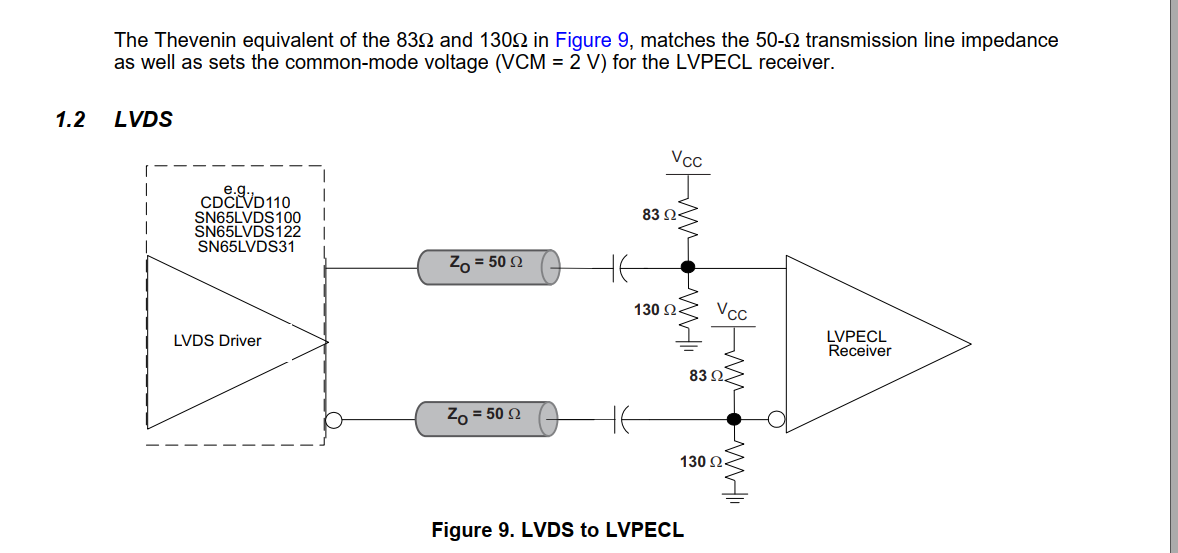

?夏醒醒 是的 那LVDS转LVPECL这个可以直接用吧?

那LVDS转LVPECL这个可以直接用吧? 升东日旭

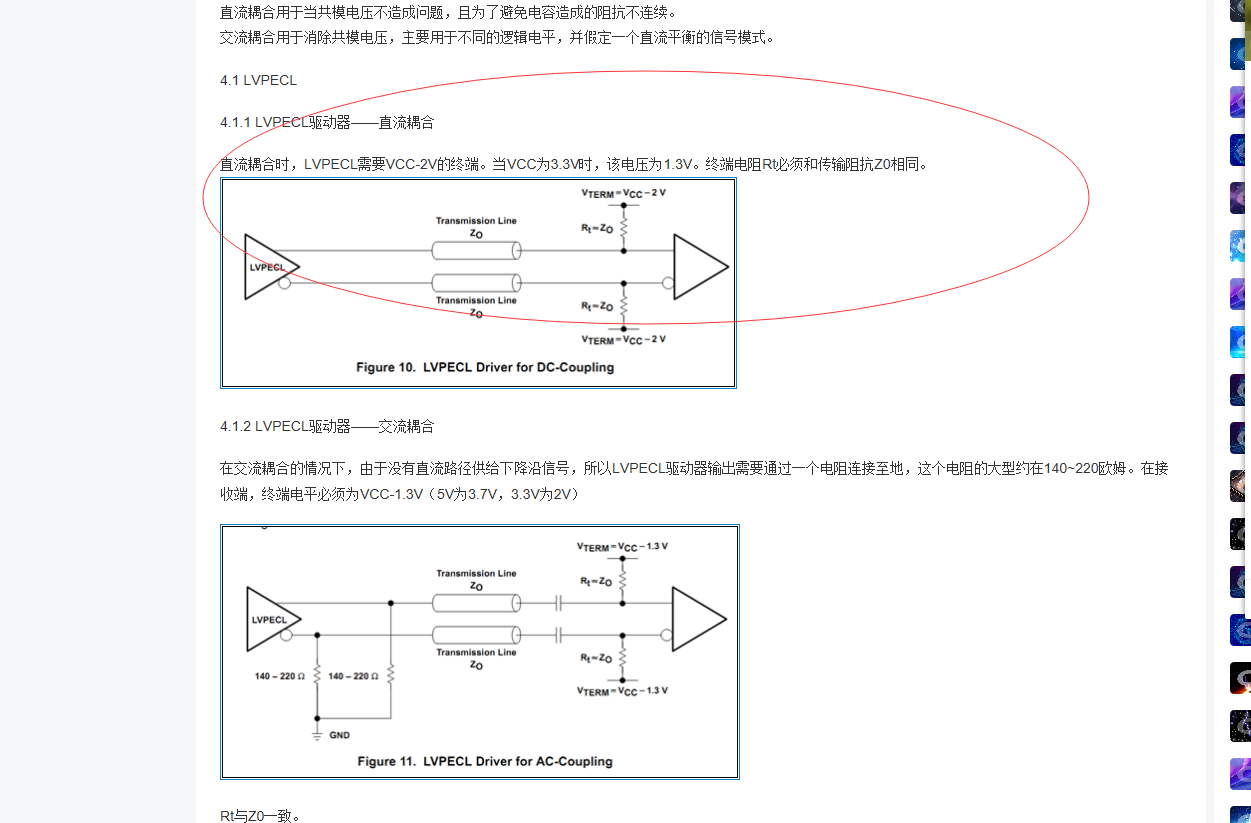

可以,这文档有问题,LVPECL的共模电平是VCC-1.3,偏置电平是VCC-2

就是输出哪个分压的值是VCC-2

水若善上

?旭日东升 不太明白,你是说LVPECL转LVDS那个有问题?

升东日旭

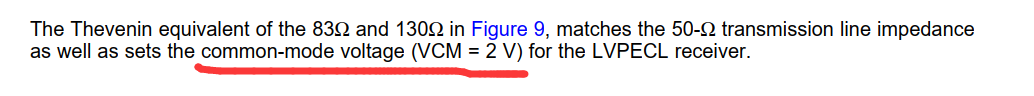

这句话有问题

这句话有问题水若善上

那这电阻值

不对?

刚刚我问一个前同事

他也说不对

水若善上

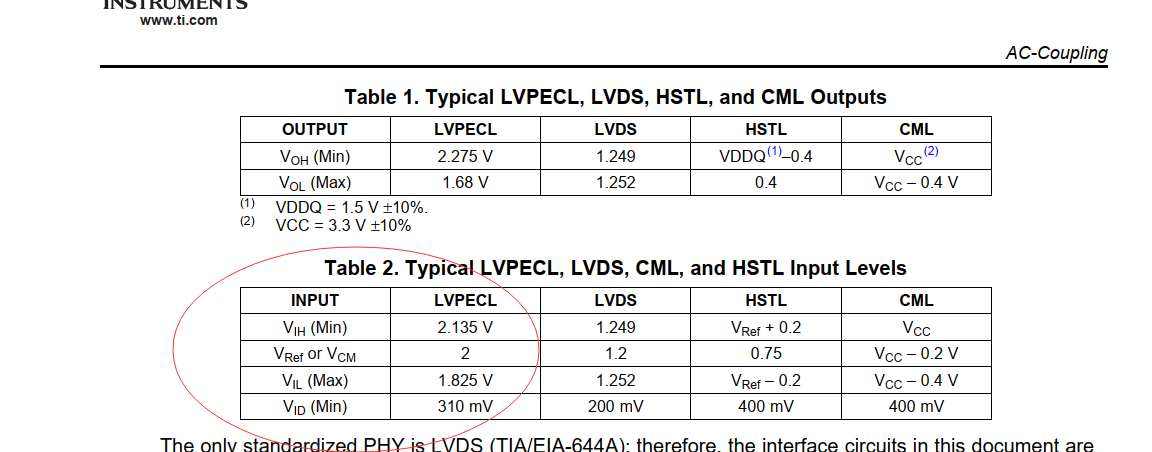

这个文档写的 LVPECL工模电压2V不对??旭日东升 抱歉,模电忘了,最近打算补补课问的问题比较啥,见谅

这个文档写的 LVPECL工模电压2V不对??旭日东升 抱歉,模电忘了,最近打算补补课问的问题比较啥,见谅升东日旭

对于3.3V系统,共模电压是2V,但是这句话讲的我理解有问题,这两个分压电阻设置的值是VCC-2,进一步说明设置一个共模电压为VCC-1.3,并不是所有额LVPECL都是共模电压2V的电平

这个你要去看下高速电路设计

模电只是基础

水若善上

?旭日东升 上午你说的其中一个问题 应该和这个有关吧?

?旭日东升 上午你说的其中一个问题 应该和这个有关吧?)000lζ/zl(sessylU.槽吐.

学渣默默的窥屏

光口手册如图

光口手册如图

那LVDS转LVPECL这个可以直接用吧?

那LVDS转LVPECL这个可以直接用吧? 这句话有问题

这句话有问题

再?一下,刚刚看你说,不是所有的LVPECL都是共模电压2v

再?一下,刚刚看你说,不是所有的LVPECL都是共模电压2v

?旭日东升 上午你说的其中一个问题 应该和这个有关吧?

?旭日东升 上午你说的其中一个问题 应该和这个有关吧?