。意随你,杯干我

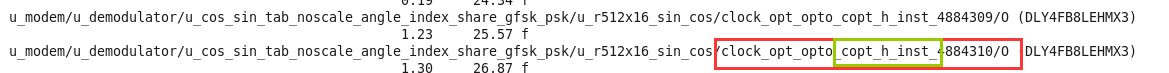

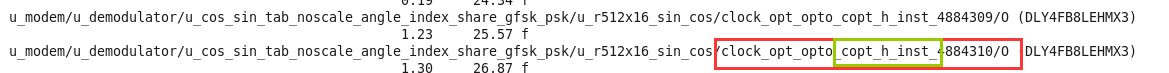

?Horizon ?Horizon 楼主有icc2各个阶段加的buffer的命名规则不 比如这个是时钟树优化时候,data path hight fanout syn的时候插的buffer?

比如这个是时钟树优化时候,data path hight fanout syn的时候插的buffer? noziroH

我不清楚这个prefix是工具自己指定的还是你的flow指定的,不过我觉得应该是后者

看名字是在CTS阶段加的

应该是flow里面自己按照下面的方式来设置的:

icc_shell> set compile_instance_name_prefix "place_opt"

icc_shell&get; place_opt

icc_shell&get; set compile_instance_name_prefix "clock_opt"

icc_shell&get; clock_opt

icc_shell&get; set compile_instance_name_prefix "route_opt"

icc_shell&get; route_opt

。意随你,杯干我

绿色的是工具加的有个h,看起来像是为了修逻辑DRC的但是place阶段并没有插入,时钟树优化的时候就插进去了。hold也没啥问题,倒是setup vio比较大place 阶段这条path没啥问题,时钟树的时候反而在data path插了好几个buffer

绿色的是工具加的有个h,看起来像是为了修逻辑DRC的但是place阶段并没有插入,时钟树优化的时候就插进去了。hold也没啥问题,倒是setup vio比较大place 阶段这条path没啥问题,时钟树的时候反而在data path插了好几个buffernoziroH

你这个是delay cell吧?

感觉是工具修Hold加进去的

。意随你,杯干我

还有好几个buffer

但是hold slack很大啊

插了好几个buffer 、delay cell,都是在时钟树的时候插的

noziroH

解data hfn在place就解了,应该不会cts去解

reEAC

SI/PI/EMC仿真分析对电子设备电磁性能设计优化非常关键,今天16点,ANSYS官方专家带你学习最新版更高效的SI/PI/EMC仿真分析新功能。→t.cn/A672M1GY

这个课程推荐给大家 免费的 。意随你,杯干我

是啊,place 阶段就是hfn了

但是hold根本没啥问题,而且slack很大

noziroH

你place阶段的logical drc如何?如果是修logical drc的话也不会选择delay cell的

。意随你,杯干我

难道copt_h的h表示修hold插的?

place阶段没drc问题的

noziroH

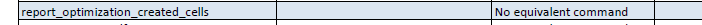

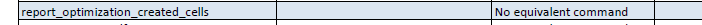

这个不清楚,不过你可以试试把它们抓出来,用下面的命令

report_optimization_created_cells -optimization_stage hold

这个是icc的,不知道icc2有没有

好吧,没有

。意随你,杯干我

真没有

真没有

比如这个是时钟树优化时候,data path hight fanout syn的时候插的buffer?

比如这个是时钟树优化时候,data path hight fanout syn的时候插的buffer? 绿色的是工具加的

绿色的是工具加的

真没有

真没有